在集成电路制造中,晶圆良率就是完成所有工艺步骤后测试合格的芯片的数量与整片晶圆上的有效芯片的比值1。

简介最终良率主要由每一步工艺的良率的积组成,从晶圆制造,中测,封装到成测,每一步都会对良率产生影响,其中晶圆制造因为工艺复杂,工艺步骤多步(300步左右)成为影响良率的主要因素。

由此可见,晶圆良率越高,同一片晶圆上产出的好芯片数量就越多,如果晶圆价格是固定的,那好芯片数量就越多就意味着每片晶圆的产量越高,每颗芯片的成本越低,那么理所当然,利润也就越高。

对于先进的集成电路芯片而言,大多数的工艺步骤都必须非常接近才能保证有高的整体良率。通常在一个新工艺或新产品刚开始之初,整体的良率都不会很高。但随着生产的进行和导致低良率的因素被发现和改进,则良率就会不断地被提升。现产品、新工艺或是工具,每个几个月或甚至几周就会被引进,因此提升良率就成了半导体公司的一个永不停息的过程1。

晶圆良率分析很多半导体公司都有工程师专门从事良率提高的工作,在晶圆厂(foundary)有专门的良率提高(YE)部门的良率工程师负责提高晶圆的良率,在无晶圆公司(Fabless)的运营部门有产品工程师(PE)要负责提高良率。由于领域有所不同,这些工程师所专注的重点也会有所区别。晶圆厂内的良率工程师对制造工艺十分精通,主要通过公司的良率管理系统(YMS)对工艺相关的一些数据进行良率分析,一般有以下几种方法:

1.产线中缺陷扫描数据(Inline Defect Scan)

2.工艺监控测试数据(WAT)

3.产线量测数据(Metrology)

4.设备共同性(Tool Commonality)

5.工艺规范性(Process Specifications)

6.失效分析(Failure Analysis)

无晶圆公司的产品工程师则对自己的产品非常熟悉,掌握一些设计数据和很多测试数据,所以产品工程师对良率分析会从一些几个方面开展1:

1.设计数据包括版图和电路图等(GDS,Schematic,etc)

2.电性测试数据(Wafer Probling,Final Test data)

3.Schmoo图

4.比特图(Bitmap)

5.系统级测试(System Level Test)

6.失效分析(Failure Analysis)

晶圆良率模型对于集成电路晶圆级的良率损失,通常会由以下两种模式的原因导致2。

第一类良率损失模式,在芯片的生产过程中一般由在生产机器中会有随机掉落的灰尘、颗粒,或空气中的尘埃引起,虽然这些颗粒尘埃是非常微小的肉眼不可见的,但是和集成电路的尺寸来说确已经非常巨大了。因为无法预见尘埃会附着在晶圆的那个位置,因此有的尘埃掉落在金属线之间会有几率导致短路,有的落在金属线形成过程中会导致开路,还有的会引起电阻、电容等电性参数的变化,因而会导致芯片功能失常而导致的良率降低。由这类问题导致的良率损失在比较大工艺结点的制程(线宽较大),或低端工艺(制程简单)中所占的良率损失的比例较大。因为这类工艺,一般对工艺设计没有很大难度,而且由于线宽较大,对工艺误差的容忍性也比较大,因此由工艺设计缺陷所导致的良率损失就比较少。

导致第一类良率损失模式的缺陷主要来自于机台日常维护不到位,例如清洗设配时没有清理干净,更换零部件时安装不仔细等,还有外界环境影响和人员在生产机台附近的异常活动也有可能导致这类良率损失。

对于第一类良率损失模式的研究在上世纪60年代就已经开始了,有很多国外和台湾的学者们分别提出了各种良率预测模型,早期的研究工作主要集中在寻找良率和线上缺陷的关系上,并用此预测模型来寻找影响良率的关键工艺步骤和机台。

表1 以缺陷为因子的良率预测模型(第一类良率损失)

第二类良率损失模式,集成电路在设计过程中的缺陷也会导致良率的降低。由于在整个芯片制造的流水线上至少有上百道工艺,而且每一道工艺都可能在几台甚至十几台相同的机台上完成,有的机台是同型号的,有的机台是不同配置的甚至连机台设计原理都完全不同。而且每台机台由于供电、供水、供气、真空度、机台设计等各种原因会有自己本身的工艺波动,而机台和机台之间由于维护手法、使用年限、人为操作等原因还存在着机台与机台间的波动。这些复杂的因素共同组成了芯片制造环境的不确定性。经过不同道工艺的不确定性叠加,最终对产品的质量参数会产生一定的影响。

当芯片的设计技术要求较低时,即线宽较大,产品规格限较宽时,这种问题比较少反应出来,因为那时产品对制成能力的容忍度比较高,及时机台有些偏差,设计的容错性也能完全吸收这些误差。而随着芯片设计要求的提高,尤其是14nm及以下的先进技术节点中,工程师发现机台能力的进步往往跟不上技术的提高,因而制成产品容错性越来越差,对工艺能力的要求越来越高,工艺设计的问题因而慢慢凸显出来,对良率的影响也越来越大。第二类良率损失模式也慢慢超过第一类良率损失模式,成为导致良率损失的元凶,特别是一些新研发的工艺技术和新的更小技术结点的结合,更容易导致第二类良率损失。如果说第一类良率损失是由于外界的随机波动导致的,那么第二类良率损失则更多的是由工艺本身固有的能力不足导致的2。

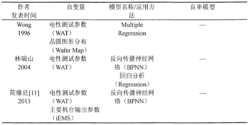

表2 以电性测试参数为因子的良率测设模型(第二类良率损失)。

本词条内容贡献者为:

黎明 - 副教授 - 西南大学

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国