基本概念

PU、MCU及DSP等电子器件中的加法运算是最基础、最常见的运算方法,常见加法器是位并行的,在一个时钟周期内完成加法运算。由于传统加法器位数有限,所以传统计算机能运算的数值范围是有限的,能精确到的浮点数位数是有限的。如果将传统加法器设计为位串行行操作,利用多个时钟周期完成一次加法运算,即输入操作数和输出结果由并行输入/输出改为随时钟串行输入/输出,比如由低到高串行输入0101和1001到位串行加法器,输出结果就是1110由低位到高位输出的数字波形,则其运算结果就可以存入FIFO或RAM 中,这样不仅能够提高加法器处理数值的上限,而且也能减少硬件资源的应用。

串行加法器即加法器执行位串行行操作,利用多个时钟周期完成一次加法运算,即输入操作数和输出结果方式为随时钟串行输入/输出。位并行加法器速度高,但是占用资源多。在许多实际应用中并不需要这样高的速度,而是希望减少硬件资源占用率,这时就可以使用位串行加法器。

串行加法器设计1位串行加法器

二进制数的加法过程是从最低位开始的,低位决定进位数:1和1相加就进1,其他进位0。下一位操作数与上一位进位决定本位相加结果:进位和操作数中1的个数不大于1则进位为0,否则进位为11。

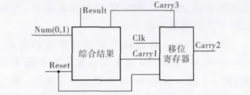

位串行加法器采用输入时钟Clk来控制加法器的操作,其逻辑如图1所示,输入信号Num(0,1)代表两个加法操作数Num(0) 和Num(1);Reset是复位端,低电平时复位;Clk 是同步时钟;Carry1、Carry2和Carry3是Num(0) 和Num(1)对应位相加的进位结果。要完成整个加法操作,主要是进位和本位操作数相加,而进位结果是由低位决定的。所以本位运算结果输出后,必须保留进位到下两位操作数到来,这样操作数才能实现和上一位进位结果一起运算。由于最低位没有进位,它的处理方式稍有特殊:在上电复位后Carry3为0,所以可以用该时刻的0作为最开始两位操作数的进位,具体操作步骤如下:

a.Num(0) 和Num(1) 的求和结果与进位结果,通过组合逻辑电路分别输出到Result 端和Carry1。

b.Clk上升沿到来后Carry1才赋值给Carry2,Carry2 移位至Carry3;Clk下降沿到来时,重复上次移位操作,此时Carry3就是第一位操作数的进位。

c.操作数第二位输入与Carry3求和,回到步骤a。依此循环,直到结果输出完毕。

2位串行加法器

在数字串行加法器中,字长为W的操作数被分为P个位宽为N(N能被W整除,P=W/N)的数字,然后从低位开始相加,在P个时钟内完成加法操作。P个时钟周期称为一个采样周期(Sample Period)。

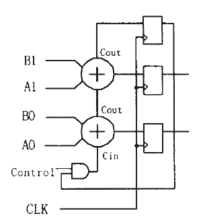

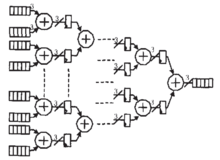

2位串行加法器,即N=2的串行加法器结构如图所示:

如果输入操作数的字长为8,那么串行加法器可以在4个时钟周期内完成加法运算。这个加法器只用了两个全加器的资源,比一般的8bit行波进位加法器小。

数字串行加法器的控制也比较简单,输入移位寄存器完成并行-串行转换功能。通过移位操作不断为加法器提供位宽为N的操作数;control信号指示了新采样周期的开始,此时carry清零;输出移位寄存器完成串行-并行转换,输出计算结果。

对于特定的输入字长,通过选择不同的N,可以实现速度、面积不同的数字串行加法器。这样,设计者可以根据实际情况加以选择,提高了设计的灵活性2。

应用

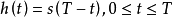

数字串行加法器可以代替传统加法器用在滤波器、乘法器、累加器等电路的设计中,能大大减小资源占用。下面以在CDMA/WCDMA系统中广泛应用的匹配滤波器为例说明数字串行加法器的应用。匹配滤波器是一种无源相关技术.它可以快速实现相关器的功能。匹配滤波器的冲激响应为:

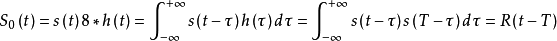

设s(t)为输入波形,则其输出波形为:

可知滤波输出R(t-T)是输入信号的自相关函数。

CDMA、WCDMA等系统中,匹配滤波使用本地码系列来匹配输入到接收机的采样数据。在滤波器中,本地码序列与接收数据进行相乘、求和操作,得到相关值,相关值越大说明相笑程度越高。

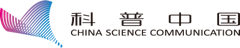

采用一般加法器实现的设计中用到的加法树有256个7bit输入,计算结果为15bit,资源消耗过大。为了减小资源消耗、提高设计密度,数字串行加法器列加法树进行改进,改进后的结构如图所示:

由于减小了加法器的运算宽度,大大降低了使用的逻辑资源。使用数字串行加法树完成加法运算需要的时钟周期与加法器的位宽有关,增加加法器的位宽可以减小运算需要的时钟局期、提高滤波器的数据吞吐量,但是也

增加了硬件资源的消耗,所以在处理能力满足的条件下,应该选择比较小的位宽。

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国