概述

80386是Intel公司1985年推出的32位微处理器,与8086、80286在目标代码级向上兼容。它具有32位宽的外部、内部数据通路和地址总线,可寻址4千兆字节的物理空间和64兆兆字节的虚拟空间。80386的显著特点是片内存储器管理机制,可实现段式、页式或段页式管理。在其后推出的80486 CPU,是在80386 CPU基础上增加了浮点运算部件和高速缓存部件。1

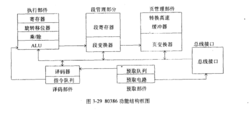

内部结构386 CPU由六个并行的功能部件组成:总线接口部件、指令预取部件、指令译码部件、执行部件、段管理部件和页管理部件。

总线接口部件:使CPU与外部总线相连接,控制进出CPU的所有地址、数据和控制信号。

代码预取部件:负责从存储器内取指令,并将预取的指令代码放到预取队列中。

指令译码部件:从预取代码队列中取出指令并翻译成微代码。

执行部件:执行从指令队列来的指令或与其它功能部件协作完成指令。

段管理部件:在执行部件有访问存储器的请求时将逻辑地址转换成线性地址。

页管理部件:负责将线性地址转换成物理地址,并把物理地址送往总线接口部件。

以上六个部件可并行和独立操作,从而大大加快了CPU处理指今的速度。1

存储器组织方式386中的基本存储单元是一个字节。一个字(16位)被存储在存储器的两个连续单元中,低字节在低地址,高字节在高地址。一个双字(32位)存储在存储器的四个连续单元中,最低字节在最低地址,最高字节在最高地址。一个字或双字的地址,是由它们的最低字节地址指定的。此外,80386还支持两种更大的存储器单位:段和页。

存储器分段是8086就采用的数据结构,它是贯穿PC微计算机系统的一个重要基本概念。80386的存储器可以分为1个或多个可变长度的段。

80386还支持分页,它将存储器组织成一个或多个4K字节的页。系统程序员可利用分页概念在多任务、多用户的操作系统中有效地管理系统的物理存储器。

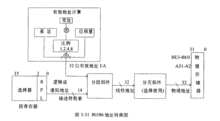

由80386 CPU组成的微机系统有三种不同的地址空间:逻辑地址、线性地址和物理地址。逻辑地址(也称为虚拟地址)由一个选择器和一个偏移量组成。选择器是某一段寄存器的内容,偏移量由寻址方式决定。

分段部件将逻辑地址空间转换成32位线性地址空间,如果不允许分页部件操作,则这个32位的线性地址就是物理地址。分页部件将线性地址空间转换为物理地址空间。

80386 CPU对存储单元的寻址方法仍然是段基地址+段内偏移量。与8086不同,这里都是32位,其中段基地址由段寄存器选择确定。段内偏移也称有效地址EA,由以下四种元素任意组合相加而成:

位移量(在指令操作码之后的一个8位或32位值);

基址(任何通用寄存器均可用作基址寄存器);

变址(除ESP外,任何通用寄存器均可用作变址寄存器);

比例因子(给变址寄存器提供一个比例因子,可以是1、2、4或8);

作为最一般的情况,EA由下式给出:EA=基址寄存器+(变址寄存器x比例因子)+位移量。1

工作方式80386 CPU有三种工作方式:保护方式、实地址方式和虚拟8086方式。

实地址方式是CPU复位后的工作方式,对程序员而言,工作在实地址方式的386 CPU实际上是具有扩充的指令系统和寄存器的高速8086 CPU。保护方式是386 CPU固有的方式,用于支持多任务运行环境,从而使PC/386具备了小型机的主要特征,较之8086有了质的提高。也正是在保护模式基础上产生了OS/2,XENIX,Windows等多任务操作系统。从程序员观点看,实地址方式和保护方式的主要区别在于地址空间和寻址机构的不同。

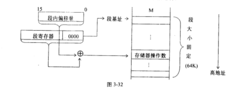

实地址方式下段寄存器的内容就是段地址,分段部件将它左移4位形成20位的段基址,然后再加上16位的段内偏移量形成线性地址,不使用分页部件,该线性地址就是物理地址,它与8086 CPU是完全相同的。

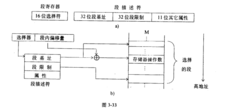

在保护方式下,段基址是32位的,但80386 CPU中段寄存器仍然是16位(为了与8086兼容)。因此,某个段寄存器的内容就不再是段的基地址,32位的段基址存放在一个表(段描述符表)中,段寄存器的内容作为选择器,即用作该表的索引,可以从表中取出相应的段描述符(包括32位段基址、段限制和存取属性等)。把从表中取出的32位段基址与32位段内偏移地址相加,在不采用分页管理时,形成32位物理地址。在保护方式下,段寄存器的内容演变为间接性的段选择符,而不再是直接的段基址,这样每个要访问的段都要事先定义一个描述符。

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国